What is a Verilog testbench ?

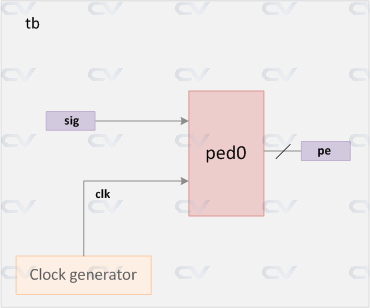

A Verilog testbench is a simulation environment used to verify the functionality and correctness of a digital design described in the Verilog hardware description language (HDL).

The purpose of a testbench is to provide a way to simulate the behavior of the design under various conditions, inputs, and scenarios before actually fabricating the physical hardware. It allows designers to catch bugs, validate functionality, and optimize designs without the cost and time associated with physical prototyping.

Verilog is a hardware description language (HDL) used for designing digital circuits and systems. Writing Verilog code with a consistent and organized style is important to make the code maintainable, readable, and error-free.

Verilog coding style can have a significant impact on the synthesis process, where your high-level Verilog code is converted into a gate-level netlist that can be implemented on an FPGA or ASIC. A well-structured and organized Verilog codebase can lead to more efficient synthesis with less hardware, and save area and power.

A singleton object refers to an instance of a class that is designed to have only one instance throughout the entire simulation runtime. In other words, a singleton object is a class instance that is shared and accessible from different parts of your verification environment, ensuring that there is always a single instance of that object.

What is uvm_component ?

uvm_component is a fundamental base class that serves as the foundation for all UVM components like drivers, monitors and scoreboards in a verification environment. It has the following features:

- Hierarchy: Supports a hierarchical structure, where each component can have child components, forming a tree-like structure and provides methods for searching and traversing the tree.

- Phasing: Components can participate in the UVM phasing mechanism, which organizes the simulation into different phases like build, connect, run, and cleanup. Components can perform specific tasks during each phase.

- Reporting: Components can use the UVM messaging infrastructure to report events, warnings, and errors during simulation.

- Factory: Components can be registered with the UVM factory mechanism, enabling dynamic object creation and lookup.