What is synthesis ?

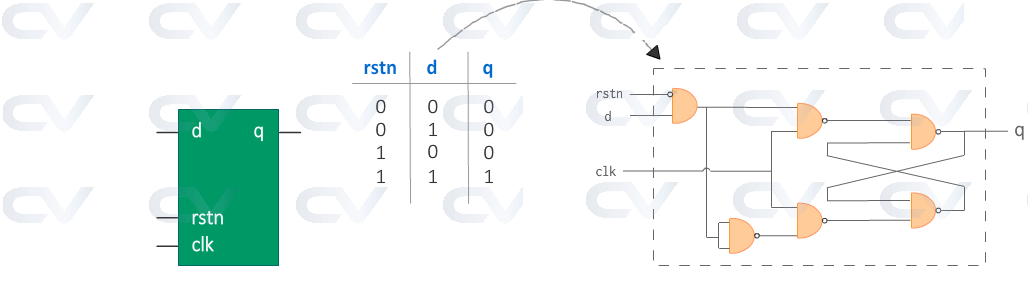

Verilog synthesis is the process of transforming high-level Verilog code, which describes digital circuits, into a lower-level representation that can be implemented in hardware. This transformation typically results in a netlist, which consists of logical components like gates and flip-flops that can be physically realized in an FPGA or ASIC.

What are Verilog Macros ?

Verilog macros allow you to define a piece of code that can be reused throughout your design. When a macro is invoked, it gets replaced by its defined content during compilation. This capability is especially useful for defining constants, parameterized expressions, or frequently used code snippets.

Syntax

The basic syntax for defining a macro is as follows:

`define MACRO_NAME [ (arguments) ] macro_body

Compiler directives in Verilog are special instructions that control how the Verilog compiler processes the code. They start with a grave accent (`) and do not require a semicolon at the end.

These directives can affect the compilation process across multiple files and are not limited to a single module. Compiler directives should ideally be placed outside of module declarations for clarity and better organization. They remain effective from their declaration point until overridden by another directive or until the end of the file.

What is a callback ?

The uvm_callback class serves as the base class for user-defined callback classes. Typically, a component developer creates an application-specific callback class by extending this base class. In the derived class, the developer defines one or more virtual methods, collectively known as the callback interface, which provide the hooks that users can override.

A callback is useful because it allows a flexible and modular way to modify or extend the behavior of a system without altering the original code. Callbacks decouple the code that triggers an action from the code that defines the action itself. It is required in scenarios where customization, or dynamic behavior is necessary.

What is a callback ?

A callback lets you give a function to someone else’s program. When that program reaches a certain point or condition, it "calls back" your function and runs it, without needing to know exactly what your function does. It’s a way for different parts of a system to work together more flexibly, without being tightly connected or dependent on each other.